## Let's Meet – Inside the Campus

26 September 2023

Presented by: Mohaddaseh Nikseresht

### Outline

- Let's Explore who I am

- Introduction

- Bitflips

- Software Protection Techniques

- A look into my PhD

- Overview

- References

Basics

I love to play video games.

### And I love chicken.

is my pet. name is "The Lady"

Hometown: Shiraz, Iran

Academic background

I studied **Computer Engineering** at **Shiraz university.** One of the **highest-ranked public** universities in Iran.

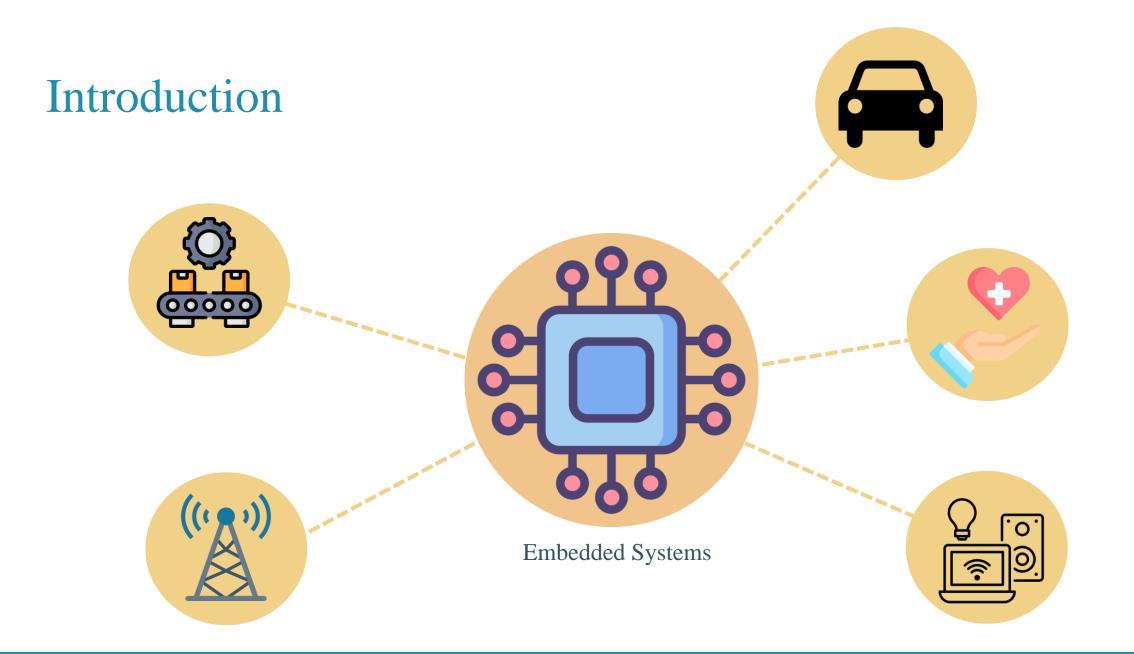

My interest in **embedded systems** began ...

In 2019, I have graduated as ranked one with several publications in well-known conferences and journals.

6

Academic background

In 2021, I have started to pursue my PhD at KU Leuven, under Supervision of **Prof. Jeroen Boydens**.

### Almost three years into my PhD ...

# Introduction

### Introduction

Advance in technology made it possible to build electronic components which are:

- Programable (+)

- efficient (+)

- cost-effective (+)

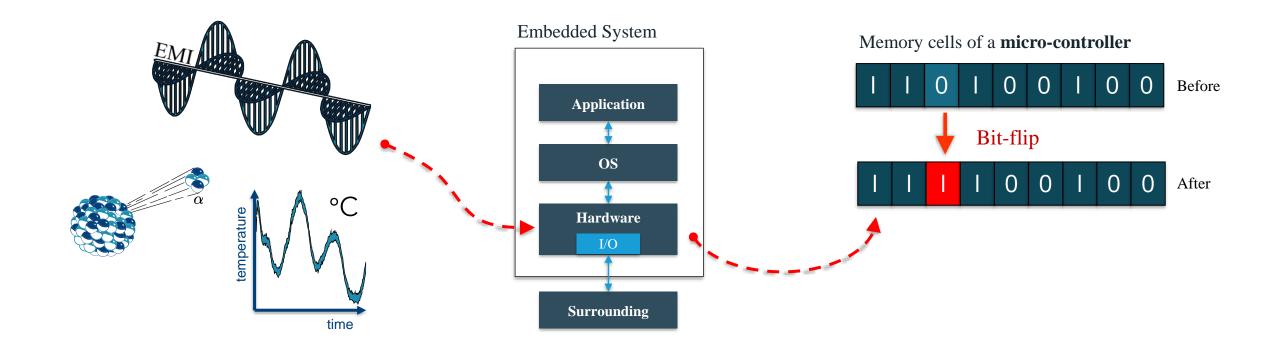

However, these changes lead to limit the processor systems' reliability byShrinking of transistor sizes (-)

**Soft Errors (Bitflips)**

Increase registers vulnerability to radiation-induced Single Event Effects (SEE)

| Different types of software errors: $0 \ 0 \ 1$ Original value |      |     |     |    |      |      |     |                |                |      |            |

|----------------------------------------------------------------|------|-----|-----|----|------|------|-----|----------------|----------------|------|------------|

| Different types of software errors:                            |      |     |     |    |      |      | 0   | 0 1            | Original value |      |            |

|                                                                |      |     |     |    |      |      | 0   | <b>1</b> 1     | Modified value |      |            |

|                                                                |      |     |     |    |      |      |     |                |                |      |            |

| 1d0:                                                           | MOV  | r3, | rO  |    | 1d0: | MOV  | r3, | rO             | 1d0:           | MOV  | r3, r0     |

| 1d2:                                                           | CBZ  | r0, | 1e2 |    | 1d2: | CBZ  | r0, | 1e2            | 1d2:           | CBZ  | r0, 1e2    |

| 1d4:                                                           | MOVS | rO, | #0  |    | 1d4: | MOVS | r0, | #0             | 1d4:           | MOVS | r0, #0     |

| 1d6:                                                           | SUBS | r2, | r3, | #1 | 1d6: | SUBS | r2, | r3             | 1d6:           | SUBS | r2, r3     |

| 1d8:                                                           | ADDS | r3, | r1  |    | 1d8: | ADDS | r3, | r1             | 1d8:           | ADDS | r3, (r1)   |

| 1da:                                                           | ADD  | r0, | r0, | #1 | 1da: | ADD  | rO, | rO, <b>#</b> 1 | 1da:           | ADD  | rO, rO, #1 |

| 1de:                                                           | BNE  | 1d6 |     |    | 1de: | BNE  | 1d6 | *              | 1de:           | BNE  | 1d6        |

| 1e0:                                                           | ADD  | r0, | #1  |    | 1e0: | ADD  | r0, | #1             | 1e0:           | ADD  | rO, #1     |

| 1e2:                                                           | BX   | lr  |     |    | 1e2: | BX   | lr  |                | 1e2:           | BX   | lr         |

Original program

Control Flow Error (CFE)

Data Flow Error (DFE)

#### Protecting embedded systems

#### Hardware techniques

Adding extra physical component to the system to increase the reliability of the system.

# Software Protection Techniques

### Software Protection Techniques

#### Protecting embedded systems

#### Protected code

#### **Pros and Cons**

- Flexible and can be automated (+)

- Suitable for COTS systems (+)

- Extra code size Overhead imposed on the system (-)

- Execution time of the application may be increased (-)

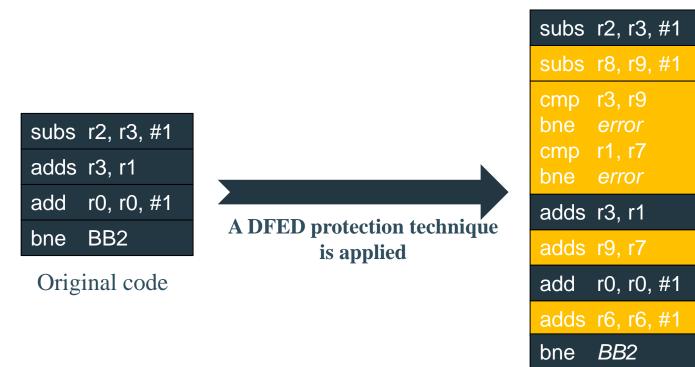

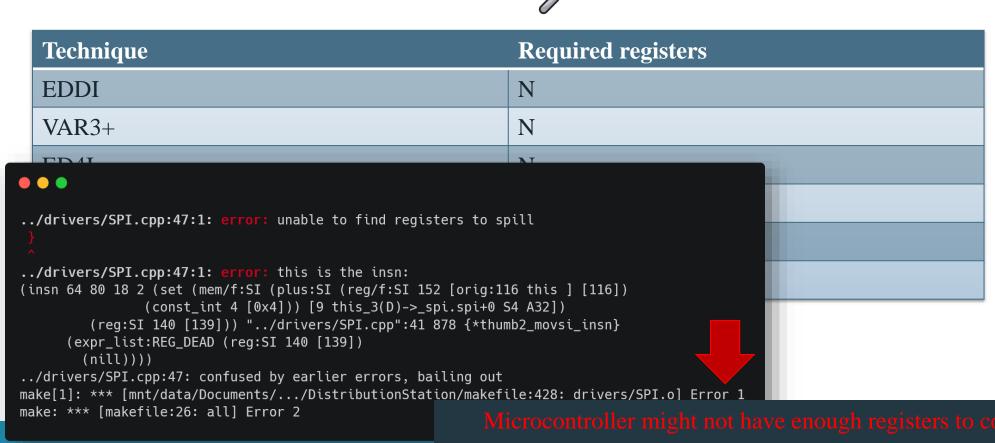

### Software Protection Techniques

Required registers for DFED techniques

Several researches have been done...

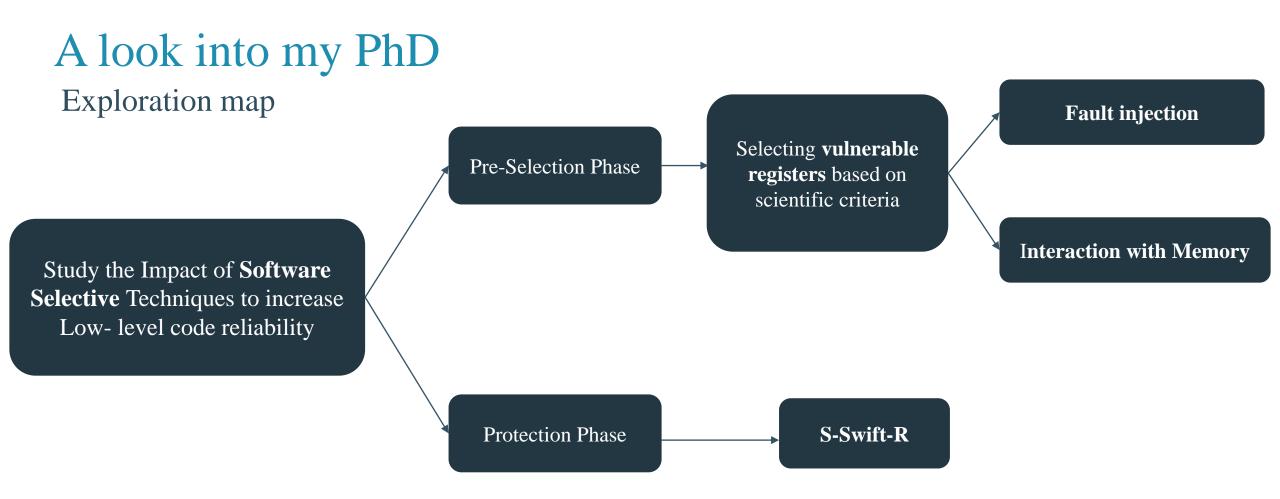

A look into my PhD: Selective Implementation of Software Resilience Techniques to Increase Low-Level Code Reliability

### A look into my PhD

Selective Protection

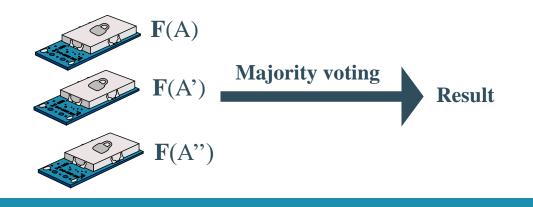

#### **Software Redundancy**

Software Implemented Hardware Fault Tolerance (SIHFT)

- Give systems the ability to detect and correct faults (+)

- Memory usage (-)

- Storage usage (-)

#### **SOLUTION:** Partially protecting the registers

### A look into my PhD

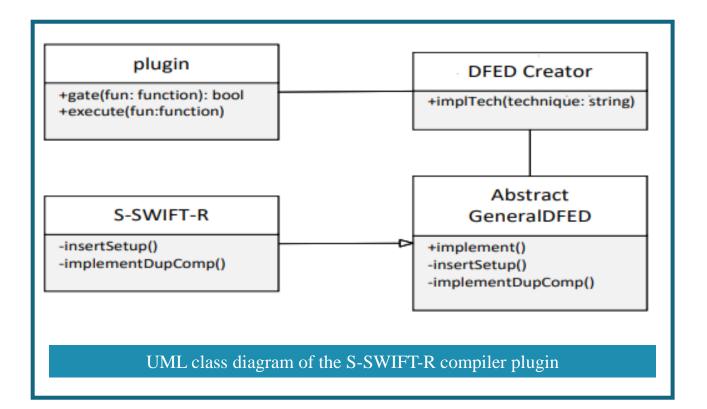

Protection phase - Automatic Implementation

# A look into my PhD

#### Example

|    |                       | Selective              | SWIFT-R                |                             |  |

|----|-----------------------|------------------------|------------------------|-----------------------------|--|

| #  | Non-Hardened          | Protected register: s0 | Protected register: s1 | Protected registers: s0, s1 |  |

| 1  | LOAD s0, 00           | LOAD s0, 00            | LOAD s0, 00            | LOAD s0, 00                 |  |

| 2  |                       | create s0 copies       |                        | create s0 copies            |  |

| 3  | LOAD s1, 2A           | LOAD s1, 2A            | LOAD s1, 2A            | LOAD s1, 2A                 |  |

| 4  |                       |                        | create s1 copies       | create s1 copies            |  |

| 5  |                       |                        | majority voter for s1  | majority voter for s1       |  |

| 6  | ADD s0, s1            | ADD s0, s1             | ADD s0, s1             | ADD s0, s1                  |  |

| 7  |                       | ADD s0', s1            |                        | ADD s0', s1                 |  |

| 8  |                       | ADD s0", s1            |                        | ADD s0", s1                 |  |

| 9  |                       | majority voter for s0  |                        | majority voter for s0       |  |

| 10 |                       |                        | majority voter for s1  | majority voter for s1       |  |

| 11 | <b>STORE s0, (s1)</b> | STORE s0, (s1)         | STORE s0, (s1)         | <b>STORE s0, (s1)</b>       |  |

### A look into my PhD Example

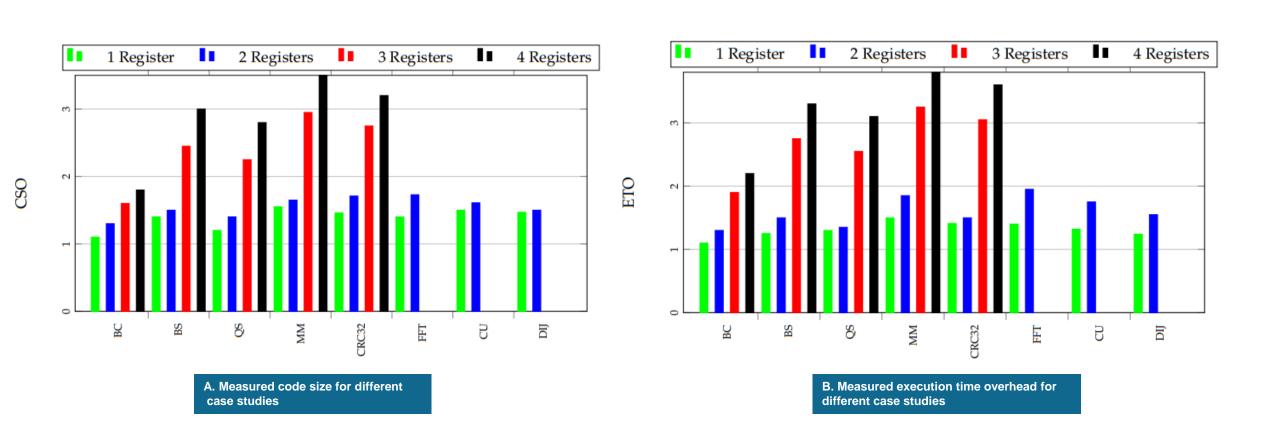

\*code size and execution time overhead increase exponentially as we increase the number of registers to protect

| Number of<br>Register     | SDC                                                   | NE                                      | Number of<br>Register     | SDC                                                   | NE                                       |

|---------------------------|-------------------------------------------------------|-----------------------------------------|---------------------------|-------------------------------------------------------|------------------------------------------|

| 1 Register                |                                                       |                                         | 2 Registers               |                                                       |                                          |

| S_SWIFT_R_F               | Min: 14.5%<br><mark>Avg.: 16.3%</mark><br>Max: 36.2%  | Min: 62.3%<br>Avg.: 72.1%<br>Max: 84.3% | S_SWIFT_R_F               | Min: 10.2%<br><mark>Avg.: 12.3%</mark><br>Max: 21.7%  | Min:69.4%<br>Avg.: 80.1%<br>Max: 88.9%   |

| S_SWIFT_R_M               | Min: 24.2%<br><mark>Avg.: 19.7%</mark><br>Max: 49.7%  | Min:50.3%<br>Avg.:66.5%<br>Max:73.9%    | S_SWIFT_R_M               | Min: 12.1%<br><mark>Avg.: 14.9%</mark><br>Max: 20.5%  | Min: 66.2%<br>Avg.: 78.6%<br>Max:79.2%   |

| Unprotected<br>(baseline) | Min: 29.1%<br>Avg.: 47.8%<br>Max: 59.34%              | Min:29.1%<br>Avg.: 41.8%<br>Max: 59.34% | Unprotected<br>(baseline) | Min:29.1%<br><mark>Avg.: 47.8%</mark><br>Max: 59.34%  | Min: 29.1%<br>Avg.: 47.8%<br>Max: 59.34% |

| 3 Registers               |                                                       |                                         | 4 Registers               |                                                       |                                          |

| S_SWIFT_R_F               | Min: 14%<br><mark>Avg.: 9.7%</mark><br>Max: 18%       | Min: 81.9%<br>Avg.: 87.3%<br>Max:89.1%  | S_SWIFT_R_F               | Min: 2.9%<br><mark>Avg: 3.1%</mark><br>Max: 4.2%      | Min: 80%<br>Avg.: 89.3%<br>Max: 90.7%    |

| S_SWIFT_R_M               | Min: 9.3%<br><mark>Avg.: 10.1%</mark><br>Max: 12.13%  | Min: 77.9%<br>Avg.: 83.2%<br>Max: 85.9% | S_SWIFT_R_M               | Min: 5.3%<br><mark>Avg.:4.1%</mark><br>Max: 6.8%      | Min: 79.3%<br>Avg. :86.1%<br>Max: 80.2%  |

| Unprotected<br>(baseline) | Min: 40.23%<br><mark>Avg.: 58.6%</mark><br>Max: 67.3% | Min: 29.8%<br>Avg.: 39.2%<br>Max: 60.9% | Unprotected<br>(baseline) | Min: 40.23%<br><mark>Avg.: 58.6%</mark><br>Max: 67.3% | Min: 29.8%<br>Avg.: 39.2%<br>Max: 60.9%  |

### A look into my PhD: Example

**KU LEUVEN**

# Overview

### Overview

- The role of Embedded systems and the impact of downscale technology on their reliability

- Bitflips:

- Definition

- Different type of Soft errors: DFE / CFE

- Hardware/ Software techniques to protect against bitflips

- Software Protection Techniques

- The Pros and Cons

- The problem of full software protection techniques

- A look into my PhD: Selective protection

- Exploration map

- $_{\circ}$  An example

### References

[1] Mohaddaseh Nikseresht, Jens Vankeirsbilck, Jeroen Boydens, A Study on Selective Implementation Approaches for Soft Error Detection Using S-SWIFT-R, Electronics, volume 11, issue 20, 21 pages, Multidisciplinary Digital Publishing Institute (MDPI), October 19, 2022

[2] Mohaddaseh Nikseresht, Jens Vankeirsbilck, Davy Pissoort, Jeroen Boydens, A Selective Soft Error

Protection Method for COTS Processor-based Systems, XXX International Scientific Conference Electronics

(ET), 2021 XXX International Scientific Conference Electronics (ET), pages 1-5, Sozopol, Bulgaria,

September 15-17, 2021

[3] Mohaddaseh Nikseresht, Brent De Blaere, Jens Vankeirsbilck, Davy Pissoort, Jeroen Boydens, Impact of Selective Implementation on Soft Error Detection Through Low-level Re-execution, DASC (Workshop),

2021 IEEE Intl Conf on Dependable, Autonomic and Secure Computing, Intl Conf on Cyber Science and Technology Congress (DASC/PiCom/CBDCom/CyberSciTech), 6 pages, AB, Canada, October 25-28, 2021

# Questions?