VLSI DCS-2020 : 2nd International Conference on VLSI Device, Circuit and System

Conference Record: 47293

Organized by,

IEEE Electron Device MSIT Student Branch Chapter

Date: July 18th-19th, 2020

( will be in Virtual Mode)

Venue: Meghnad Saha Institute of Technology, Kolkata, India

url: https://edu.ieee.org/in-msitceds/vlsi-dcs-2020/

Focal Areas:

Components, Devices, Circuits, and Systems

Welcome to 2020 IEEE VLSI-DCS, to be held in Meghnad Saha Institute of Technology (MSIT), Kolkata, India on July 18-19, 2020. The annual VLSI-DCS conference is a premier international forum for researchers, developers and users to present and discuss the cutting edge ideas on topics related to the VLSI devices, circuits and Systems. The conference is organized by IEEE ED MSIT Student Branch Chapter. The technical program will be tailored to reflect the wide spectrum of topics and research interests shared by researchers in the fields. We invite you to submit your original contributions, not presented or published or submitted anywhere in full or in part, or not under consideration.

** All the accepted and presented papers will be sent to the IEEE ffor possible inclusion in the IEEEXplore. Some of the extended version of the accepted and presented papers will be published in the special issues of the following journals,

1.Special Issue in Nanoscience & Nanotechnology-Asia, Bentham Science, Scopus Indexed https://www.benthamscience.com/journal-files/special-issue-details/NNA-SII20190415-01.pdf

2. Special issue in Journal of Mechanics of Continua and Mathematical Sciences (Emerging Sources Citation Index (ESCI)), published by IOMOCAMS http://www.journalimcms.org/

3. Special issue in International Journal of Nanoscience, World Scientific, (Emerging Sources Citation Index (ESCI))

https://www.worldscientific.com/worldscinet/ijn

4. Special Issue in Nanomaterials and Energy, ICE publishing (Emerging Sources Citation Index (ESCI))

https://www.icevirtuallibrary.com/toc/jnaen/current?=

5. Special Issue in Circuit World, Emerland Journal (ISSN: 0305-6120) (2018 Impact Factor: 1.042)

http://www.emeraldgrouppublishing.com/products/journals/call_for_papers.htm?id=8719

communication is in progress with other journals

________________________________________________________________________________

LIST OF THE SPEAKERS

Program Schedule

| IEEE VLSI DCS 2020-1ST DAY [ 18 TH JULY, 2020] | ||||

| 8.00 am- 8.30 am | Conference Registration | |||

| 8.30 am-8.45 am | Tea Beak | |||

| 8.45am-9.30am | Conference Inaguration | |||

| 9.30 am-10.15am | Plenary Talk-1 by Prof. Lance C. C. Fung, IEEE R10 EAC Chair, Emiretus Prof., Mudoch University, Australia | |||

| 10.15 am-11.00 am | Plenary Talk-2 by Prof. Wriitam Banerjee, POSTECH, South Korea | |||

| 11.00am-11.45 am | Plenary Talk-3 by Prof. Celia Sahanaz, Chair, IEEE Bangladesh Setion, BUET, Bangladesh | |||

| 11.45 am-12.00pm | Break | |||

| 12.00 pm-12.40 pm | Key Note-1 by Prof. Kohran Cengiz, Trakya University, Turkey | |||

| Key Note-2 by Dr. Amit Banerjee, NUS, Singapore | ||||

| 12.40 pm – 1.00 pm | LUNCH BREAK | |||

| 1.00 pm-3.00 pm | Track-1 | Track-2 | Track-3 | Track-4 |

| Emerging Device: Modelling and Simulations | Emerging Analog VLSI Circuits | Embedded Hardware | Circuit/System for Hiigh Speed Network | |

| 3.00pm-3.30 pm | Tea Beak | |||

| 3.30 pm-4.15 pm | Plenary Talk-4 by Prof. Benjamin Iniguej, Fellow, IEEE | |||

| 4.15 pm-4.30 pm | Break | |||

| 4.30 pm-5.10pm | Key Note-3 by Prof. Wladek Grabinsky, GMC, Switzerland | |||

| Key Note -4 by Prof. Subir K Sarkar, IEEE EDS DL | ||||

| 5.10 pm-5.30 pm | BREAK | |||

| 5.30 pm-6.30 pm | Track-5 | Track-6 | Track-7 | Track-8 |

| FPGA Based System | SENSOR DEVICE | Quantum Modelling and Simulation | Novel nano-materials and devices | |

| 6.30 pm-6.45 pm | Tea Beak | |||

| 6.45 pm-7.45pm | Tutorial-1 by Dr. Sreetama Ghosh, Competence Centre for Catalysis, Chalmers University of Technology, Sweden | |||

| Tutorial-2 by Dr. Atri Mukhopadhyay, CONNECT Centre, Trinity College Dublin | ||||

| 7.45 pm-8.00pm | Break | |||

| 8.00 pm-9.00pm | Tutorial-3 by Mr. Sankalp Jain, SoC Implementation Engineer, Apple, Austin, USA | |||

| IEEE VLSI DCS 2020-2ND DAY [ 19TH JULY, 2020] | ||||

| 8.00 am- 8.30 am | Conference Registration | |||

| 9.00 am-9.45 am | Tutorial-5 by Dr. Ananda Sankar Chakraborty, Berkeley Wireless Research Center;University of California Berkeley;California, USA | |||

| Tutorial-6 by Dr. Binit Syamal, Nanyang Technological University, Singapore | ||||

| 9.45 am-10.00am | Tea Break | |||

| 10.00 am-10.40 am | Key Note-5 by Dr. Arindam Biswas, Kaji Najrul University | |||

| Key Note-6 by Prof. Jyotsna Kumar Mondal, Kalyani University | ||||

| 10.40 am-11.20 am | Key Note-7 by Prof. Amlan Chakraborty, Calcutta University | |||

| Key Note-8 by Prof. Ajit Kumar Panda, IEEE EDS DL | ||||

| 11.20 am-12.00 pm | Key NOTE-9 by Dr. Soumya Pandit, IEEE R10 EDS Vice Chair | |||

| Key NOTE-10 Prof Debaprasad Das, Professor, Assam University | ||||

| 12.00 pm – 1.30 pm | Lunch Break | |||

| 1.30 pm-3.30 pm | Track-9 | Track-10 | Track-11 | Track-12 |

| Optoelectronics/Photovoltaic Device and Circuit | Devices for Low Voltage Application | Ciruits/System for AI/ML | Energy Efficient Ciruits/System | |

| 3.30pm-4.00 pm | Tea Beak | |||

| 4.00 pm-5.30pm | Track-13 | Track-14 | Track-15 | Track-16 |

| Quantum Circuits | Advanced Nanomaterials | Advanced CMOS and Beyond CMOS Devices | Low Power Device | |

| 5.30 pm-5.45 pm | Break | |||

| 5.45 pm- 6.00 pm | Valedictory Session | |||

Details of the Tracks

| Track 1:Emerging Device: Modeling and Simulations Session Chair: Prof.(Dr.) D Nirmal, Karunya University, India Session Co-chair: Dr Kalyan Biswas,MCKV Institute of Technology,India |

BSH SEMINAR ROOM | 18/07/2020 | 1:00 PM | 3:00 PM | Estimation of Power and Delay of CMOS Phase Detector and Phase-Frequency Detector using nano Dimensional MOS Transistor |

| Analytical modeling for parasitics in a triple gate MOSFET device | |||||

| Gate Engineered GAA Silicon-Nanowire MOSFET for High Switching Performance. | |||||

| Study of device performance of dual metal gatee silicon on insulator MOSFET adopting Various dielctric material in gate oxide | |||||

| Mathematical Modelling of Drain Current Enhancement in High-k FD MOSFET | |||||

| Impact of Dopant variations on Junctionless Cylindrical Nanowire FETs | |||||

| Impact of Graded Back-Barrier on Linearity of Recessed Gate InAlN/GaN HEMT | |||||

| Analytical Drain Current Model for super-threshold region of Double Gate Tunnel FET | |||||

| Track 2: Emerging Analog VLSI Circuit Session Chair:Prof. (Dr.) Rajnish Sharma, Chitkara University, India Session Co-chair: Prof. (Dr.) Arpan Deyasi,RCC Institute of Information Technology,India |

EE SEMINAR ROOM | 18/07/2020 | 1:00 PM | 3:00 PM | Design Of High Performance Digital Divider |

| A 2.5mW Low-Power Dual VCO Quantizer for ∑-∆ Modulator in 0.09μm CMOS | |||||

| Design of Low Phase-Noise LC- VCO at 2.5GHz by Body-Bias Technique using CMOS 180 nm Technology | |||||

| Comparative Study of Doublet OTA Circuit Topologies Operating in Weak Inversion Mode for Low Power Analog IC Applications | |||||

| Multi Input Single Output using Operational Transresistance Amplifier as First Order Filter | |||||

| Design of Telescopic OTA based 6th order Butterworth Low Pass Filter using 0.18μm CMOS Technology | |||||

| Design of a Wideband differential RF-Amplifier using Indigenous 180nm digital CMOS Technology | |||||

| Low-power and Area Efficient Approximate Multiplier with Reduced Partial Products | |||||

| Track 3: Embedded Hardware Session Chair:Prof. (Dr.)Pradip Kumar Ghosh, Techno India New Town, India Session Co-chair:Dr Sudip Dogra, Meghnad Saha Institute of Technology, India |

VLSI DESIGN LAB | 18/07/2020 | 1:00 PM | 3:00 PM | Automated System Design for the Identification of Sleep Disorder: Cross-correlation and SVM Based Approach |

| Intellectual Completion Tracking System micro-architecture for Advanced NoC Designs | |||||

| A CAD Approach for Accurate Decap Estimation and Allocation for Supply Noise Reduction in SoC | |||||

| EEG Based Mental Arithmetic Task Classification Using a Stacked Long Short Term Memory Network for Brain- Computer Interfacing | |||||

| Secured MPFAL Logic for IoT Applications | |||||

| Wide Input Range Differential Dual Band RF Energy Harvesting System for Battery-Less RFID Applications | |||||

| Verilog Modeling of 24 Bit Stereo DAC Using Multibit SDM | |||||

| Ultra Low-voltage, Low-power Fourth-order Butterworth LPF for ECG Signal Processing | |||||

| Track 4:Circuit/System for High Speed Network Session Chair:Prof. (Dr.) Debaprasad Das, Assam University, India Session Co-chair:Dr Surajit Bari, Narula Institute of Technology, India |

ECE SEMINAR ROOM | 18/07/2020 | 1:00 PM | 3:00 PM | Design of Modified Grounded Microstrip Antenna for Dual Band operation in Wireless Communication |

| Design of Low power & High Performance Multi Source H-Tree Clock Distribution Network | |||||

| Multi-Stage-Multi-Iterative Optimization Algorithm for Design Optimization of Multi-Quantum Well Terahertz Avalanche Transit Time Sources | |||||

| Design of Inline Coaxial Probe to RGW Transition in Ku and K Band | |||||

| UHF RFID Spectrum detection threshold of the secondary user for CSI certainty | |||||

| A Low-Power gm-C Filter for Neural Signal Conditioning | |||||

| 15W Hybrid GaN Power Amplifier through Microstrip Radial Stub 4W GaN MMIC for X-band Radar Applicaions | |||||

| Development of 14nm tri-layered (s-Si/s-SiGe/s-Si) Channel DG- NanoFET | |||||

| Track 5: FPGA Based System Session Chair: Dr Tridibesh Nag, Netaji Shubhas Engineering College, India Session Co-chair: Dr Swarnil Roy, Meghnad Saha Institute of Technology, India |

BSH SEMINAR ROOM | 18/07/2020 | 5:30 PM | 6:30 PM | FPGA-Based Digital Down Converter for GSM Application |

| FPGA Implementation of WRVFLN for Classification | |||||

| Realization of Built-In Self Test(BIST) enabled memory(RAM) using VHDL and implemetation in Spartan6 FPGA board | |||||

| FPGA Implementation of Symmetric Systolic FIR Filter using Multi-channel Technique | |||||

| Track 6:Sensor Device Session Chair: Dr Shubhankar Majumdar, NIT Meghalaya, India Session Co-chair:Dr Subhashis Roy, Techno India University, India |

EE SEMINAR ROOM | 18/07/2020 | 5:30 PM | 6:30 PM | Significance of Different Buffer Layers in an SPR Multichannel Sensor |

| Advantages of Charge Plasma Based Double Gate Junction-less MOSFET over Bulk MOSFET for Label Free Biosensing | |||||

| TCAD Analysis and Modelling of Gate-Stack Gate All Around Junctionless Silicon NWFET based Bio-Sensor for Biomedical Application | |||||

| Evaluation of Selectivity and Sensitivity of Heterostructure Junction-Less DG-MOSFET Based Biosensor Considering Heating Effect | |||||

| Track 7: Quantum Modelling and Simulation Session Chair: Dr Arindam Biswas, Kaji Najrul University, India Session Co-chair:Dr Papiya Debnath, Techno India New Town, India |

VLSI DESIGN LAB | 18/07/2020 | 5:30 PM | 6:30 PM | Performance Evaluation of a Double Gate Pentacene Organic FET using Simulation Study |

| First-principle study of spin transport in GaAs-Adenine-GaAs semi-conductor tunnel junction | |||||

| Performance analysis of sub-10nm vertically stacked gate-all-around FETs | |||||

| Electronic Properties of Fluorine Functionalized Germanene Nanoribbons | |||||

| Track 8: Novel nano-materials and devices Session Chair:Prof (Dr) Arghya Majumdar, Kaji Najrul University, India Session Co-chair: Dr Chandan Kumar Pandey, VIT-AP University, India |

ECE SEMINAR ROOM | 18/07/2020 | 5:30 PM | 6:30 PM | A novel single-component Fractional-order capacitor based on Graphene Nanosheet/P(VDF) composite: Synthesis and Analysis |

| Synthesis and Characterization of Fe Doped CdS Quantum Dot | |||||

| Correlation between I-V and bonding network of Fe3O4_rGO nanocomposite | |||||

| Spectral Tuning of Gold Nanoparticles Embedded in Dielectric by Changing Anisotropy and Interparticle Interaction: A Mathematical Correlation between the Shape and Interaction | |||||

| Track 9: Optoelectronics/Photovoltaic Device and Circuit Session Chair: Prof (Dr) Rishu Chaujar, DTU, India Session Co-chair: Prof (Dr) Utpal Ganguly, Meghnad Saha Institute of Technology, India |

BSH SEMINAR ROOM | 19/07/2020 | 1:30 PM | 3:30 PM | TCAD based optimization of SJ Infrared solar cell for an efficient thermo-photovoltaic application |

| Analysis of all optical Dual control Dual SOA TOAD based 2’s Complement generator | |||||

| Far field profile estimation in mono mode step index optical fiber with Kerr type nonlinearity by a simple technique | |||||

| Computing Cut-off Wavelengths from Dispersion Characteristics for 2D Triangular Photonic Crystal based Superlens | |||||

| Kerr Nonlinearity Effect on Dimensionless Scalar and Vector Propagation Constants of Single-Mode Graded Index Fiber: Estimation by a Simple but Accurate Method | |||||

| Harmonic Compensation for Nonlinear Loads Fed by Grid Connected Solar Inverters Using Active Power Filters | |||||

| Three Input NAND gate using Semiconductor Optical Amplifier | |||||

| Design of Photonic Filter using Metamaterial based Defected Ternary Structure under Normal Incidence | |||||

| Track 10: Devices for Low Voltage Application Session Chair: Prof (Dr) Angsuman Sarkar, Kalyani Govt. Engineering College, India Session Co-chair: Dr Farooq Khanday, University of Kashmir, India |

EE SEMINAR ROOM | 19/07/2020 | 1:30 PM | 3:30 PM | Performance Analysis of a Novel Hetero-material InAs/GaAs Junctionless TFET. |

| Analytical model and simulation based analysis of a doped Si DG TFET exhibiting lower subthreshold slope | |||||

| Stepped Gate Profiles over DRE TFET: A Proposal to Improve Off-State Breakdown Voltage | |||||

| Double Gate p-n-p-n TFET with Hetero Oxide Dielectric and High-K Spacer Engineering | |||||

| Current Reference circuit operable at Low voltages using Composite MOS Triode Resistor | |||||

| Sub-threshold Performance Analysis of Multi-Layered Trapezoidal Trench Gate Silicon On Nothing MOSFET for Low Power Applications | |||||

| The Effect of Gate Stack and High-ĸ Spacer on Device Performance of a Junctionless GAA FinFET | |||||

| Effect of Body Thickness on Device Performance of Graded Channel TMDG Stack Gate TFET | |||||

| Track 11: Ciruits/System for AI/ML Session Chair: Prof. (Dr) Jyotsna Kumar Mondal, Kalyani Govt. Engineering College, India Session Co-chair: Dr. Chandi Pani, Meghnad Saha Institute of Technology, India |

VLSI DESIGN LAB | 19/07/2020 | 1:30 PM | 3:30 PM | Power Allocation in NOMA using Cournot Game Theory |

| Optimizing FANET Routing using a Hybrid approach of Firefly Algorithm and ACO-Lévy flight. | |||||

| GPSO Hybrid Algorithm for Rectilinear Steiner Tree Optimization | |||||

| Attenuation Modelling and Machine Learning Based SNR Estimation for 5G Indoor Link | |||||

| Design and implementation on EMBA Authentication models | |||||

| Fuzzy PID Controlled DSTATCOM for Deliveing Quality Power | |||||

| Performance Analysis of Hybrid Electro-Optic Architecture for Next Generation Network | |||||

| Design and implementation of eye pupil movement based PIN authentication system | |||||

| Track 12: Energy Efficient Ciruits/System Session Chair:Prof. (Dr) Rajarshi Mahapatro, IIIT Naya Raipur, India Session Co-chair: Dr. Swapnadip De, Meghnad Saha Institute of Technology, India |

ECE SEMINAR ROOM | 19/07/2020 | 1:30 PM | 3:30 PM | Automatic Generation Control in Restructured Power System with Capacitive Energy Storage and Communication Delay Based Cascaded Controller |

| Intelligent Energy Management Systems for Optimal Techno-Commercial Benefit in DC Micro-grids: A review | |||||

| Stability Analysis of Electric Vehicle Integrated Microgrid for Power Frequency Balance | |||||

| Differential Evolution Algorithm Based Energy Management of Residential Microgrid under Appliance Scheduling DSM | |||||

| Improved Loss Characteristic in 1-bit RF MEMS Switch owing to Lower Dielectric Constant | |||||

| A Non-Invasive Approach for Fetal Arrhythmia Detection and Classification from ECG Signals | |||||

| Chaotic Advection using Universal Motor Drive | |||||

| Computing Overlapping Signal Influence on Gain Characteristics of EDFA | |||||

| Track 13: Quantum Circuits Session Chair:Prof (Dr) Sumanlata Tripathi, Lovely Professional University, India Session Co-chair:Dr. Sutirtha Kumar Guha, Meghnad Saha Institute of Technology, India |

BSH SEMINAR ROOM | 19/07/2020 | 4:30 PM | 5:30 PM | Simulation of Triple Gate Spin Field-Effect Transistor and its Applications to Digital Logic |

| Design of 3:2 Compressor Using Quantum Dot Cellular Automata | |||||

| Design of Multiplexer Using Actin Quantum Cellular Automata | |||||

| Low Power Quaternary Adder using CNFET | |||||

| Analysis of all-optical XNOR gate in SOA based tree-net architecture | |||||

| Stability of Hybrid SET-CMOS based NOT gate | |||||

| Track 14: Advanced Nanomaterials Session Chair:Dr. Bikash Sharma, Sikkim Manipal Institute of Technology, India Session Co-chair:Dr. Abhigyan Ganguly, University of KwaZulu Natal, Durban, South Africa. |

EE SEMINAR ROOM | 19/07/2020 | 4:30 PM | 5:30 PM | Conduction Mechanism of Polyaniline/Reduced Graphene Oxide/Ag2O Nanocomposite |

| Comparative Study between Silica gel- Aluminium & Crystalline silica – Aluminium Composites Developed through P/M Route | |||||

| Performance analysis of Ni3GeFe2 / Fe3GeTe2 composites as ferromagnetic layer in MTJ memory devices | |||||

| Determination of Structural, Electronic, Optical and Mechanical Properties of Brookite TiO2 Using Various Exchange-Correlation | |||||

| Charge transfer mechanism of Gallium Nitrite/Reduced Graphene Oxide (GaN/rGO) nanocomposite. | |||||

| Development of Aluminium Based Magnetic Composites & Study on Chemical Properties at Sea Water Environment | |||||

| Track 15: Advanced CMOS and Beyond CMOS Devices Session Chair:Dr. Ankush Ghosh, School of Engineering and Applied Sciences, The Neotia University, India Session Co-chair: Prof. Biswajit Ganguly, Meghnad Saha Institute of Technology, India |

VLSI DESIGN LAB | 19/07/2020 | 4:30 PM | 5:30 PM | Analytical Modeling of Asymmetric Junctionless DMDG MOSFET for Suppressing Short Channel Effects |

| An Evolutionary Approach based Optimization of Small Signal Parameters for GSDG MOSFET | |||||

| Effect of Channel Doping and Fin Shapes on Performance of Junctionless bulk FinFET | |||||

| Exploration of Stepped Recessed Gate Silicon-On-Nothing MOSFET for Enhancing Self Heating Effect | |||||

| Performance Analysis of FinFETs with Strained-Si Fin on Strain-Relaxed Buffer | |||||

| High Speed Buried Channel In0.53Ga0.47As/InP MOSFET with Corner Spacer for Low Power Applications | |||||

| Track 16: Low Power Device Session Chair:Prof (Dr) N Mohankumar, GITAM school of Technology, Bengaluru Campus, India Session Co-chair:Prof Shubrapratim Nath, Meghnad Saha Institute of Technology, India |

ECE SEMINAR ROOM | 19/07/2020 | 4:30 PM | 5:30 PM | Design of Area Optimized Arithmetic and Logical Unit for Microcontroller |

| Impact of Temperature on Circuit Performances of Junctionless MOSFET in Sub-threshold Regime | |||||

| Design and Analysis of Bulk and Junctionless MOSFET Based Circuits for Low Power Applications | |||||

| Investigation of Comparator Architecture in 32nm Silicon-On-Insulator(SOI) Technology | |||||

| Investigation on quadruple gate FinFET structure in absence of all the corner metal gate regions | |||||

| Design and Analysis of Double Gate Tunnel Field Effect Transistor using Charged Plasma |

Call for Paper (CFP)

Topics of particular interest include, but are not limited to:

Track A: VLSI Devices

Device Modelling and Simulations,, Optoelectronic Devices and Displays, MEMS, Sensors and Imagers, Power Devices, Deeply Embedded Devices and technology, Characterization, Reliability and Yield, Compound Semiconductors and High Speed Devices, Process and Manufacturing Technology, Memory Devices, Emerging devices, Neuromorphic Devices and Device Concepts, Low Power Devices and Circuits, Advanced CMOS and Beyond CMOS Devices, Photovoltaic Devices, Emerging natural and nature-inspired materials, Advanced CMOS and Beyond CMOS Devices for application in Microsystems, Logic synthesis and finite automata, Circuit and Device Interactions, Biodegradable and Flexible electronic Devices, Electron Devices for “More than Moore”, Role of Electron Devices in Transforming Surface Transportation, synthesis and verification of integrated circuits and systems of any complexity

Track B: Nanotechnology:

Novel nano-materials and devices, Nanobiotechnology, Nanomaterials for energy conversion, Green nanotechnology, Nano Mechanics, Carbon Nanotubes emitters, Biological applications of nanoparticles, Energy applications of nanomaterials, Nano Fabrication and Metrology, Nano Heat Transfer and Energy Information Technology, Nano Sensors, Actuators and Systems Nanobionics, Nanofluidics and Bio Chips, Organic Electronics, Organic field-effect transistors (OFETs), organic electrochemical transistors (OECTs), proton transistors.

Track C: Analog/Digital/Mixed VLSI Circuits:

Analog and Mixed Signal Integrated Circuits, Amplifiers, Filters, Comparators, Oscillators, Multipliers, PLLs, RF ICs, Voltage/Current References, Sample-And-Hold Circuits, A/D and D/A Converters, High Speed IO Interface, Energy Harvesting, Power Management, Wireless Transceivers and RF/mm-Wave Circuits, Low Power Circuits and systems, Circuits in Sub-threshold and Near threshold regime, Digital Integrated Circuits, SOC, and NOC, Linear and Non-linear Circuits, Bio Chips; MEMS/NEMS circuitry, Standalone memory circuits: DRAM, FLASH, Quantum Modeling, chaos/neural/fuzzy-logic Circuits, novel I/O circuits for advancing data rates, improving power efficiency, and supporting extended voltage applications, clocking techniques including PLLs and CDRs components such as equalizers, high-speed ADC-RX/DAC-TX, silicon photonic and optical interface circuitry.

Track D: VLSI Systems : Embedded system: architecture, design, and software; System architectures: NoC, 3D, multi-core, and reconfigurable; Memory System; FPGA designs, FPGA based systems; CAD: synthesis and analysis, Prototyping, verification, modeling, and simulation; imagers, displays, sensors and biomedical and healthcare applications; IoT including ultra-low power, energy harvest, wearable,sensors, display, and communication devices Big Data, Machine learning Algorithm; Wireline and Optical Communications Circuits and Systems for electrical and optical communications including serial links for intra-chip and chip-to-chip interconnections,high-speed memory and graphics interfaces, backplanes, long-haul, and power line communications; flexible, printed, large-area and organic electronics. system in package, 2.5D, 3D and monolithic 3DIC, multi-die heterogeneous integration, silicon photonic interconnects and packaging, advanced assembly and bonding, embedded cooling technologies, Efficient electrical system, Reconfigurable computing, Cluster Computation, High Performance Distributed Computing (HPDC), parallel and/or distributed computing techniques, parallel processing, distributed computing systems and computer networks.

Track E: VLSI Algorithm, Design & Testing :

Analog/Mixed-Signal/RF Test, ATPG & Compression, Embedded System & Board Test, Embedded Test Methods Emerging Technologies Test, FPGA Test, Silicon Debug, Automotive Test & Safety, Built-In Self-Test (BIST) Defect & Current Based Test, Defect/Fault Tolerance, Delay & Performance Test, Design for Testability (DFT) Design Verification /Validation, Fault Modeling and Simulation, Hardware Security, Low-Power IC test , Microsystems / MEMS /Sensors Test, Memory Test and Repair, On-Line Test & Error correction, Power / Thermal Issues in Test, System-on-Chip (SOC) Test, Test Standards, Test Economics, Test of Biomedical Devices, Test of High-Speed I/O, Test Quality and Reliability, Test Resource Partitioning, Transients and Soft Errors 2.5D, 3D and SiP Test.

Paper Submission Guidelines and Proceedings

1.Paper Submission Guidelines and Proceedings

• Paper length must be maximum five pages of A4 size paper including figures and references. Its content must be original and unpublished

• Manuscript must be prepared to conform IEEE Conference format, e.g. font type, size, column, etc. Accepted paper/s must be registered and presented at the conference.

• If an author has got more than one accepted papers, each paper has also to be registered. Papers (pdf ) are to be submitted via Easy Chair Conference System.

Paper Submission link: https://easychair.org/conferences/?conf=ieeevlsidcs2020

2.Paper review process:

After submission, the paper enters into the review process. VLSI DCS 2020 research papers are reviewed using a single-blind process managed through EasyChair. A committee of reviewers selected by the Technical Committee will review the documents and rate them according to quality, relevance, correctness, and originality. The review process of research papers (full papers and short papers) for VLSI DCS 2020 will be a two-round process. Papers are reviewed on the basis that they do not contain plagiarized material and have not been submitted to any other conference at the same time (double submission). In the first round, papers are reviewed independently by a minimum of three members of the conference Technical Program Committee (TPC). No outside reviewing is used for In the first round, papers are reviewed independently by a minimum of three members of the conference Technical Program Committee (TPC). No outside reviewing is used for VLSI DCS 2020. Criterions for the peer reviewed proceess,

- Scope and subject relevance: Is the article appropriate for this publication?

- Novelty of the work: Is this original material distinct from previous publications?

- Validity: Is the study well designed and executed?

- Data analyss: Are the data reported, analyzed, and interpreted correctly?

- Clarity in writings: Are the ideas expressed clearly, concisely, and logically?

- Clarity in figures/tables/graphs: Are the graphs/figures/tables expressed clearly, concisely with good resolution?

- Advancement: Is this a significant contribution to the field?

- Completeness of the references

Registration

According to IEEE VLSI DCS 2020 conference registration policy, after obtaining the formal acceptance by e-mail, at least one author of each paper must complete registration formalities including payment of full registration fees at the rate mentioned below. Participants are requested to read all the information displayed below carefully.

| Member | Amount for Indian Author (INR) |

Amount for International Authors (USD) |

|

Non-IEEE Members from Academia and Industry |

4000 |

200 |

|

IEEE Members from Academia and Industry |

3500 |

150 |

| IEEE Student Members (only UG) (All authors must be student)* |

2500 |

100 |

|

Non-IEEE Student Members (only UG) (All authors must be student) |

3000 |

150 |

| Accompanying Person | 2500 |

100 |

* as per IEEE Registration Fee Requirements

It is mandatory for one of the authors for each paper to register in advance and present the paper for inclusion in the conference proceedings. According to IEEE’s No-show policy, it is up to the discretion of the Conference Committee to allow “no shows” to be published in the IEEE Xplore Digital Library.

•It is mandatory for one of the authors for each paper to register in advance and present the paper for inclusion in the conference proceedings.

•To register as a student member, all the authors must be student members.

•Registration fee excludes accommodation. The outstation participants requiring accommodation may have a look at the links present in the bottom of our conference website to hire rooms.

•Research scholars will not be considered as any category of student.

•Registration fee is non-refundable.

•Registration is required for each accepted paper separately.

•If an author has more than one accepted paper, he has to register each paper separately.

•If co-authors want to participate, they have to register as “Accompanying Person”.

Details for online payment of the registration fee:

Name – Meghnad Saha Institute of Technology

*After submitting the registration fee via online transfer, authors needs to submit the followings,

- Receipt of the conference fees // in pdf or image format//

- Abstract of the paper // in MS doc format//

- Camera ready papers based on the review report // In DOC and PDF//

- Details of the online transaction in separate doc file

Instruction for the registered Authors:

IEEE VLSI DCS 2020 will carry the registration and payments of the registered authors, the entire feee will be forwarded to the new event date. Please reach out with any questions

for registration related issues: manash@msit.edu.in ( +91 98300 59765 )

Important Dates

(Revised due to rescheduling of the Conference)

Full paper submission date: 15th April, 2020 (closed)

Notification of acceptance date: 20th June, 2020

Registration of the accepted papers: 30th June, 2020 (closed)

Camera ready Submission : 30th June, 2020

Committee

Chief Patrons:

Mr. Satyam Roy Chowdhury, Managing Director, Techno India Group

Mr. Tapan Kumar Ghosh, Exceutive Director, Techno India Group

Dr. Sanku Bose, GCEO, Techno India Group

Patrons:

Prof. (Dr.) Ankur Ganguly, Prinncipal, MSIT

Prof. (Dr.) Sukumar Ray Chaudhuri, Director, MSIT

Prof. (Dr.) Susanta K. Bhattacharya, Director, Academic Quality Assurance, TIG

General Chair:

Dr. Manash Chanda, Vice Chairman, IEEE ED Kolkata Chapter and Chapter Advisor, IEEE ED MSIT Student Branch Chapter

General Co-Chair:

Dr. Sudip Dogra,Former HOD, Associate Professor, Dept. of ECE, MSIT

Dr. Ansuman Sarkar, Chairman, IEEE ED Kolkata Chapter

Program Chairs:

Prof. Amlan Chakrobrty, Director, AKCSIT, University of Calcutta

Prof. Debasish De, Director and Professor, CSE, MAKAUT; Advisory Board Member, IEEE EDS Kolkata Chapter

Prof. Subir Kumar Sarkar (DL, IEEE EDS ) Professor., Jadavpur University, Advisory Board Member, IEEE EDS Kolkata Chapter

Program Co chair:

Dr. Soumya Pandit, Vice Chair, IEEE EDS SRC, Region 10

Dr. Mohan Kumar, Vice-Chair, IEEE EDS Region 10

Conveners:

Prof. (Dr.) Utpal Ganguly, Professor, MSIT

Dr. Chandi Pani, Associate Professor, Dept. of ECE, MSIT

Co-Convener:

Dr. Ambarnath Banerjee, Professor, Dept. of EE, MSIT

Technnical Program Chairs

Dr. Manash Chanda, Vice Chairman, IEEE ED Kolkata Chapter and Chapter Advisor, IEEE ED MSIT Student Branch Chapter

Dr. Angsuman Sarkar, KGEC, Kalyani, Immediate Past Chairman, IEEE EDS Kolkata Chapter

Dr. Swapnadip De, HOD, Dept. of ECE, Dept. of ECE, MSI, Senior Member, IEEE

Prof. Biswarup Ganguly, Member, IEEE, MSIT

Organizing Chairs:

Prof. Arpan Deyasi, Ex. Comm. Member, IEEE EDS Kolkata Chapter

Dr. Bikash Sharma, Treasurer, IEEE EDS Kolkata Chapter

Prof. Subhrapratim Nath, HOD, Dept. of CSE, MSIT

Organizing Co-Chairs:

Dr. Saheli Sarkhel, Excomm. Member, IEEE EDS Kolkata Chapter

Prof. Sudipta Ghosh, Assistant Prof., Dept. of ECE, MSIT

Prof. Indrajit Das, Assistant Prof., Dept. of IT, MSIT

Publication Chairs:

Dr. Arindam Biswas, Kaji Najrul University

Publicity Chair:

Dr. Tridibesh Nag, ExComm. Member, IEEE Kolkata Section

Dr. Papiya Debnath, TINT, Rajarhat Newtown

Finance Chairs

Mr. Sanjay Kishore Chakraborty, TIG

Mr. Arup Muhuri, MSIT

Registration Chair:

Prof. Swarnil Roy, Assistant Professor, Dept. of ECE, MSIT; Ex-Comm. Member, IEEE SSCS Kolkata Chapter

Registration Co-Chairs:

Mrs. Tanushree Ganguly, Dept. of ECE

Mrs. Saheli Chatterjee, Dept. of ECE

Organizing Committee Member :

Prof. Ruben Roy, GCELT, Kolkata

Dr. Surajit Bari, Dept. of ECE, NIT-Agarpara

Dr. Sunipa Roy, Dept. of ECE, GNIT

Prof. Souvik Goswami, Dept. of MCA, MSIT

Local Hospitality Chair:

Adrija Mukherjee, Chair, IEEE EDS MSIT SBC

Deepro Banerjee, Chair, IEEE MSIT SB

Local Hospitality Co-Chair:

Mr. Manoj Modak, Dept. of ECE, MSIT

Mrs. Shiuly Ganguly, Dept. of ECE, MSIT

Mr. Kamalendu Langal, Dept. of ECE, MSIT

Advisory Board

Prof. Benjamin Iñiguez, Universitat Rovira i Virgili, Spain, Fellow, IEEE

Mr. Deepak Mathur, IEEE R10 DIRECTOR-ELECT

Dr Lance C.C. Fung, Murdoch University, Australia, Chair, 2020 IEEE R10 EAC

Prof. (Dr) Celia Shahnaz, Department of EEE, BUET, Dhaka, Bangladesh; Chair, IEEE Bangladesh Section

Dr Wladek Grabinski, (GMC) Consultant, Switzerland

Prof. Hao Ying, IEEE Fellow, Wayne State University, Michigan, USA

Prof. Bimal K. Bose, IEEE Life Fellow, Professor, Univrsity of Tennessee, USA

Prof. (Dr.) Chandan K. Sarkar, Professor, Jadavpur University and ExChair, IEEE Kolkata Section

Dr. Korhan Cengiz, Tarkya University, Turkey

Dr. Amit Banerjee, NUS, Singapore

Prof. Hiroshi Inokawa, Shizuoka University, Japan

Prof. Mariya Aleksandrova, Dept. of Microelectronics, Technical University of Sofia, Bulgaria

Prof Lipo Wang, NTU, Singapore

Prof. Ljiljana Trajkovic, Fellow, IEEE, Simon Fraser University, Canada

Prof. Klimis Ntalianis, Associate Professor, University of West Attikca, Athens, Greece

Prof. Vijay K. Arora (DL-IEEE, USA)

Prof. G. N. Dash, IEEE EDS DL, Sambalpur Univversity, India

Dr. Ruma Kareem K. Ajeena, University of Babylon, Iraq

Prof. Rajib Kar, NIT Durgapur

Dr. Chandrasekaran Subramaniam, SKCET, Coimbatore, india

Mr. Utpal Chakraborty, Head, Artificial Intelligence, Yes Bank, Mumbai

Prof. Subir Kr. Sarkar (DL-IEEE, JU, India)

Prof. Writam Banerjee (CAS, China)

Prof. S. S. Chung (Fellow-IEEE, Taiwan)

Mr. Sankalp Jain, APPLE, USA

Mr. Saurav Haldar, Intel, Santa Clara, Carlifornia

Prof. Rajarshi Mahapatra (IIIT Raipur, India)

Mr. Avijit Pradhan, RF IC R&D Dsign Engineer, Peregine Semiconductor. USA

Prof. Debaprasad Das (AU, India)

Dr. Binit Shyamal (Global Foundry, Singapore)

Mr. Deepan Roy, Synopsis, USA

Dr. I. J. Rudras, Obuda Univrsity, Budapest, Hungary

Dr. Sreetama Ghosh, CUT, Sweden

Visa Information

The Consulate of India requires a visa application form that is completed online. To access the form follow this link: https://indianvisaonline.gov.in/visa/. Click on the orange button labeled “Regular Visa Application” in the upper-left corner to begin the process. Your application must:

- Display your name exactly as it appears in your passport

- Include answers for all fields

- Type of visa and length of validity requested must match listing on all other documentation

- Be signed on the first page under the photo, and, on the second page. In order to be accepted, all signatures must:

- Match the signature in your passport

- Be in the middle of the box. They cannot touch the edges of the box or run out of the box

- Include your email address on the online application. Applications missing a personal email address will be rejected by the consulate

- Be printed on single-sided sheets of paper. Double-sided applications will be rejected. You must fully print the bar code on the bottom of page 1

- Your passport will be shipped back to the address indicated on your application under “Present Address.”

Please read the India Visa Application Guide before you begin the online visa application form.

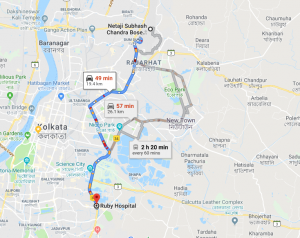

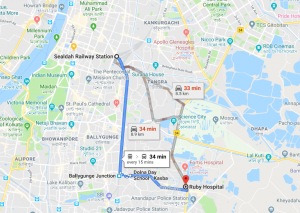

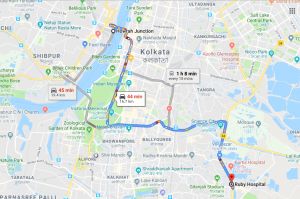

Venue Information

Meghnad Saha Institute of Technology

Nazirabad, Uchchepota

Kolkata- 700150

West Bengal

India

- Kolkata Airport to Venue

- Sealdaha Station to Venue

- Howrah Station to venue

Hotel Information

Link of Few nearby hotels are –

- Hyatt Regency, JA-1 Sector III, Salt Lake City, Kolkata, India.

- Hotel Gateway, Ruby Hospital Crossing

- J. W. Marriot, Mathpukur, E. M. Bypass

- Hotel Treebo

- Many budget hotels are also available

Please find the following links for budget hotels,

Contact

Dr. Manash Chanda

General Chair, 2020 IEEE VLSI DCS

Advanced VLSI Design Lab,

Dept. of ECE

Meghnad Saha Institute of Technology,

Nazirabad, Uchchepota, Kolkata-700150, West Bengal, India

mail id: ieee.vlsidcs@gmail.com ( for conference related query)

manash@msit.edu.in ( for urgent query)

contact no.: +91 9830059765